- Part Number Configuration Voltage Clock Rate / Access time Package Temperature SCD#

-

No record

S698PM芯片是一款抗辐照型的高性能、高可靠、高集成度、低功耗的多核并行处理器SoC芯片。S698PM采用国际最先进LEON4内核,采用对称多处理架构(SMP),遵循SPARC V8标准,专为高端嵌入式实时控制及复杂计算等应用而设计。

S698PM芯片内部集成了丰富的片上外设,包括GPIO、UART、定时器、中断控制器、调试支持单元、存储器控制器、1M/10M 的1553B总线控制器、CAN总线控制器、10M/100M以太网控制器、SpaceWire总线节点控制器、CCSDS遥控/遥测控制器、USB2.0主控器、SPI主控器、I2C主控器等功能模块。

S698PM芯片内嵌在线调试支持单元(DSU),用户可以通过JTAG、UART或以太网等接口连接DSU来访问芯片内部的寄存器、存储器和片内外设,可以方便地进行软、硬件调试和开发。S698PM芯片支持RTEMS、 eCOS、VxWorks、Linux等实时嵌入式操作系统,用户可方便地实现嵌入式实时控制系统的高性能多核并行处理设计。

S698PM芯片芯片内部所有逻辑单元具有三模冗余(TMR)加固,片内与片外存储器进行了检错纠错(EDAC)加固,芯片抗辐照指标满足高可靠、抗辐照产品要求。

S698PM芯片可广泛应用在航空、航天、电子、核工业、兵器、船舶、测控、工业控制等领域。

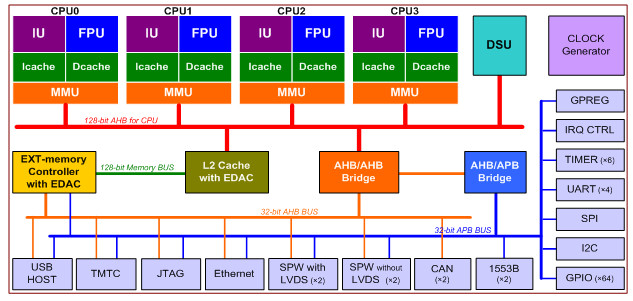

图1-1 芯片各个模块的说明如下:

1) CPU0~CPU3:4个处理器核心;

2) IU:SPARC V8整型处理单元,遵循IEEE-1754标准;

3) FPU:双精度浮点处理单元,遵循IEEE-754标准;

4) Icache:32KB指令缓存;

5) Dcache:16KB数据缓存;

6) MMU:存储器管理单元;

7) DSU:调试支持单元;

8) CLOCK Generator:时钟信号发生器;

9) Ext-memory Controller with EDAC:具有检错纠错功能的存取外部存储单元控制器;

10) L2 Cache with EDAC:具有检错纠错功能的二级缓存;

11) AHB/AHB Bridge:处理器核心互联AHB总线/片内外设AHB总线间的转换桥;

12) AHB/APB Bridge:片内外设AHB总线/APB总线间的转换桥;

13) USB2.0 HOST:USB2.0主控制器;

14) TMTC:CCSDS遥测/遥控模块;

15) JTAG:JTAG控制器;

16) Ethernet:10/100M以太网控制器;

17) SPW with LVDS:内置LVDS驱动器的SpaceWire总线节点控制器;

18) SPW without LVDS:无内置LVDS驱动器的SpaceWire总线节点控制器;

19) CAN:CAN2.0总线控制器;

20) 1553B:1553B总线控制器;

21) GPREG:通用寄存器;

22) IRQ CTRL:中断控制器;

23) Timer:定时/计时器;

24) UART:通用串行接口;

25) SPI:SPI主控制器;

26) I2C:I2C总线控制器;

27) GPIO:通用输入输出接口。

► 采用对称多核(SMP)架构体系,片内集成了4个相同的处理器核心;

► 每个处理器核心配置了:

♦ 32位SPARC V8整型处理单元(IU),符合IEEE-1754标准;

♦ 64位双精度浮点处理单元(FPU),符合IEEE-754标准;

♦ 一级缓存(含32KB指令缓存ICache和16KB数据缓存DCache);

♦ 存储器管理单元MMU;

♦ 硬件乘法器和除法器;

♦ 支持MAC和UMAC等DSP指令;

♦ 7级指令流水;

► 基于AMBA2.0标准总线的可裁减结构:

♦ 各个处理器核互联总线:128-bit带宽的AHB;

♦ 片内高速外设互联总线:32-bit带宽的AHB;

♦ 片内低速外设互联总线:32-bit带宽的APB;

♦ 128-bit AHB与32-bit AHB间的转换桥:AHB/AHB bridge;

♦ 32-bit AHB与32-bit APB间的转换桥:AHB/APB bridge;

► 两级缓存结构:

♦ L1 Cache:一级缓存,含32KB ICache和16KB DCache,位于处理器核心中;

♦ L2 Cache:二级缓存,512KB,位于外存储器控制器与128-bit AHB总线之间;

► 片内外设:

♦ 存储器控制器,支持ROM、SRAM、DDR2、MAP IO,支持32位、16位和8位的数据位宽;

♦ 中断控制器,支持片内设备中断和可编程的外部中断;

♦ 4通道的SpaceWire总线节点控制器,其中:

1. SPW0、SPW1内置LVDS驱动器;

2. SPW2、SPW3无内置LVDS驱动器,需要外扩驱动芯片;

♦ 2通道的1M/10M速率1553B总线控制器;

♦ 2通道的CAN2.0总线控制器;

♦ CCSDS 遥控遥测TM/TC模块;

♦ JTAG控制器,符合IEEE-1149标准;

♦ 10/100M自适应以太网控制器;

♦ USB2.0 HOST接口;

♦ 在线硬件调试支持单元DSU;

♦ 4个32位的通用定时器(含一个看门狗定时器);

♦ 2个带锁存功能的32位定时器;

♦ 4个通用串行接口;

♦ SPI主控制器;

♦ I2C总线控制器;

♦ 通用输入输出接口;

► 抗辐照加固设计

♦ 内部时序逻辑单元:TMR加固;

♦ 内部存储器模块:EDAC检错纠错;

♦ 外部存储器接口:EDAC检错纠错;

► 推荐工作频率范围:≤ 500MHz;

► 工作温度:-55℃~+125℃;

► 性能指标:1652DMIPS@500MHz(Dhrystione 2.1),1015MFLOPS@500MHz(Whetstone);

► 典型功耗:内核功耗≤2W@1V,500MHz;IO功耗:≤0.3W@3.3V,500MHz;DDR2IO功耗:≤0.7W@1.8V,500MHz;SpaceWireIO功耗:≤0.02W@2.5V,500MHz;

► 工作电压:

♦ 内核:1.0V±0.1V;

♦ 普通IO(除DDR2和USB的IO外):3.3V±0.3V;

♦ DDR2的IO:1.8V±0.15V;

♦ USB的IO: 2.5V±0.2V、3.3V±0.3V;

♦ SpaceWire的IO:带片内LVDS的IO口为2.5V,LVDS差分350mV;不带片内LVDS的IO口为3.3V;

► 抗辐性能:

♦ 芯片内部触发器全部采用TMR技术加固,内部存储器全部采用了EDAC技术加固,外部存储器控制器带有EDAC功能,能很好的抗单粒子翻转(SEU);

♦ TID: ≥300Krad(Si); SEL:≥99.8 MeV.cm2/mg; SEU: 优于1E-5 Error/Component/Day;

► 封装:

♦ 塑料球形阵列PBGA784,工业级,S698PM-PI,外形尺寸为37.5mm*37.5mm,球间距为1.27mm;

♦ 陶瓷柱形阵列CCGA576,陶瓷工程样片,S698PM-CE, 外形尺寸为37.5mm*37.5mm,球间距为1.27mm;

♦ 陶瓷柱形阵列CCGA576,军级,S698PM-CMM, 外形尺寸为37.5mm*37.5mm,球间距为1.27mm;

♦ 陶瓷柱形阵列CCGA576,宇航级,S698PM-CMS, 外形尺寸为37.5mm*37.5mm,球间距为1.27mm;

► 软硬件开发环境:

♦ 集成开发环境(IDE):Orion 6.0;

♦ 操作系统(EOS):VxWorks、Linux、eCos、RTEMS;

♦ 芯片应用开发系统:S698PM-DKit;

♦ 全套测试例程源码;

♦ 设备驱动接口(API)及例程。

|

序号 |

产品型号 |

产品描述 |

|

1 |

S698P4-PI |

S698P4-PI 塑料封装,PQFP208,工业级 |

|

2 |

S698P4-II-CE |

S698P4-II-CE 陶瓷封装,CQFP256,工程样片 |

|

3 |

S698P4-II-C |

S698P4-II-C 陶瓷封装,CQFP256,军级 |

|

4 |

S698P4-ASIC-IP-F |

ASIC版本固核(ASIC网表) |

|

5 |

S698P4-FPGA-IP-V |

FPGA版本固核(FPGA网表) |

|

6 |

S698P4-RTL-IP-S |

软核(RTL源码) |

s698p4-II 芯片用户手册(V2.1).pdf s698p4-II 芯片用户手册(V2.1).pdf

|

资料下载 |

S698系列处理器技术及产品白皮书V9.0 S698系列处理器技术及产品白皮书V9.0

|

资料下载 |